Презентация из 38 слайдов содержит:

- определение термина "процессор";

- подробное описание текстовое и в картинках устройства и его характеристик;

- приводятся особенности свойств некоторых процессоров.

Презентация из 38 слайдов содержит:

- определение термина "процессор";

- подробное описание текстовое и в картинках устройства и его характеристик;

- приводятся особенности свойств некоторых процессоров.

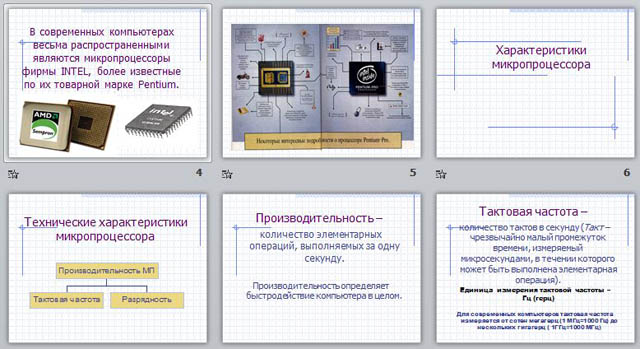

Микропроцессор

Процессор – устройство, обеспечивающее преобразование информации и управление другими устройствами компьютера («МОЗГ» компьютера)

Современный процессор представляет собой микросхему, или чип (англ. chip), выполненную на миниатюрной кремниевой пластине – кристалле. Поэтому его принято называть – микропроцессор.

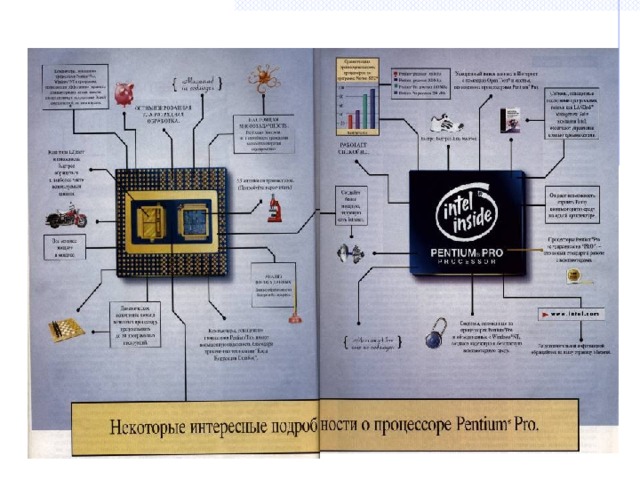

В современных компьютерах весьма распространенными являются микропроцессоры фирмы INTEL, более известные по их товарной марке Pentium.

Характеристики микропроцессора

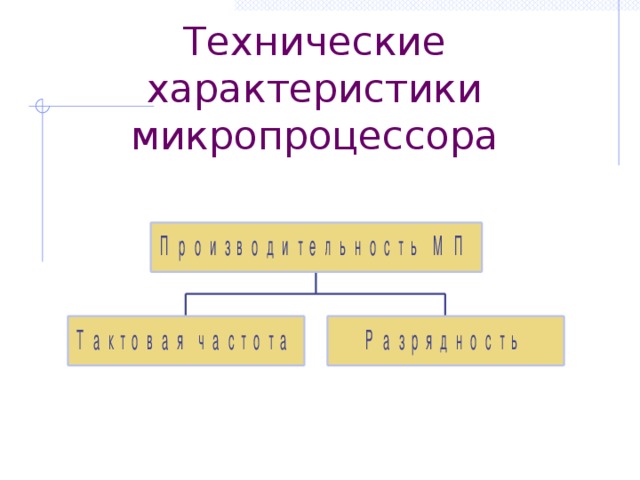

Технические характеристики микропроцессора

Производительность –

количество элементарных операций, выполняемых за одну секунду.

Производительность определяет быстродействие компьютера в целом.

Тактовая частота –

количество тактов в секунду ( Такт – чрезвычайно малый промежуток времени, измеряемый микросекундами, в течении которого может быть выполнена элементарная операция).

Единица измерения тактовой частоты – Гц (герц)

Для современных компьютеров тактовая частота измеряется от сотен мегагерц (1 МГц=1000 Гц) до нескольких гигагерц ( 1ГГц=1000 МГц)

Разрядность –

размер минимальной порции информации, обрабатываемой процессором за один такт.

Эта порция информации, часто называемая машинным словом, представлена последовательностью двоичных разрядов (бит).

Процессор в зависимости от его типа может иметь одновременный доступ к 8, 16, 32, 64 битам.

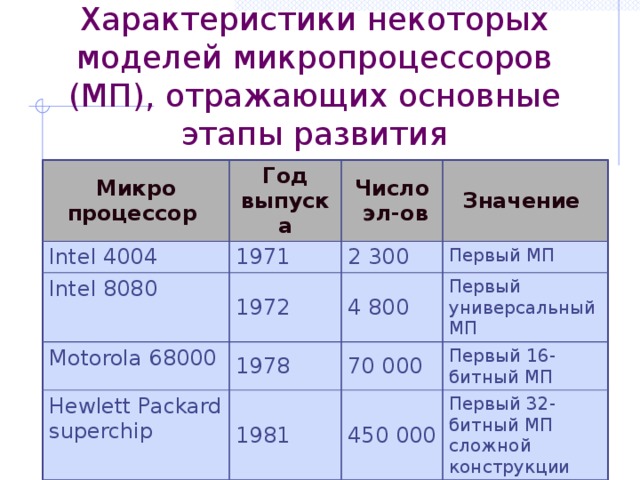

Характеристики некоторых моделей микропроцессоров (МП), отражающих основные этапы развития

Микро процессор

Год выпуска

Intel 4004

1971

Intel 8080

Число эл-ов

Motorola 68000

1972

2 300

Значение

Первый МП

1978

4 800

Hewlett Packard superchip

Первый универсальный МП

70 000

1981

Первый 16-битный МП

450 000

Первый 32-битный МП сложной конструкции

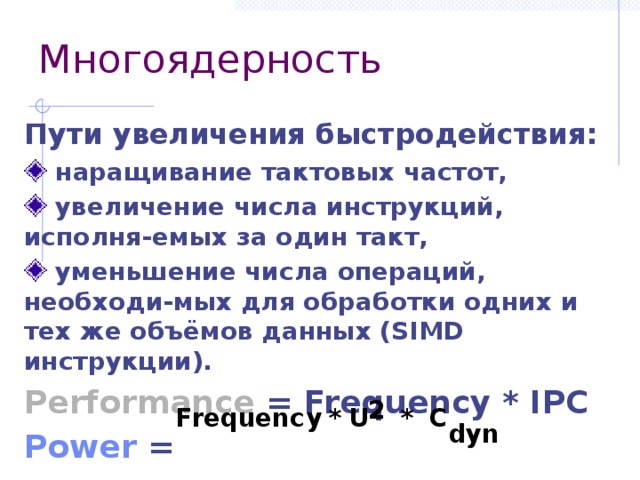

Многоядерность

Многоядерность

Пути увеличения быстродействия:

Performance = Frequency * IPC

Power =

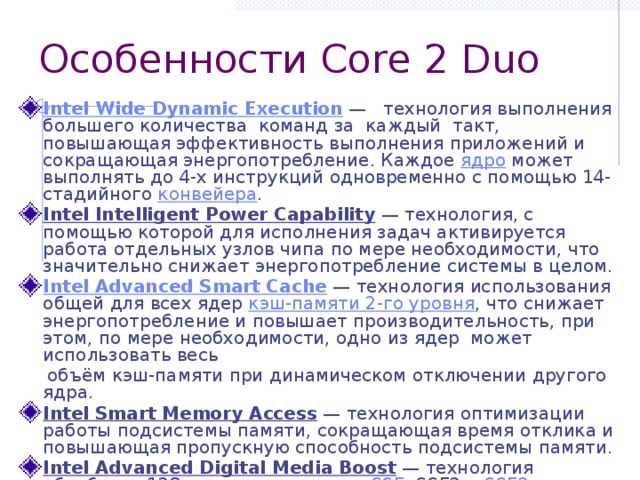

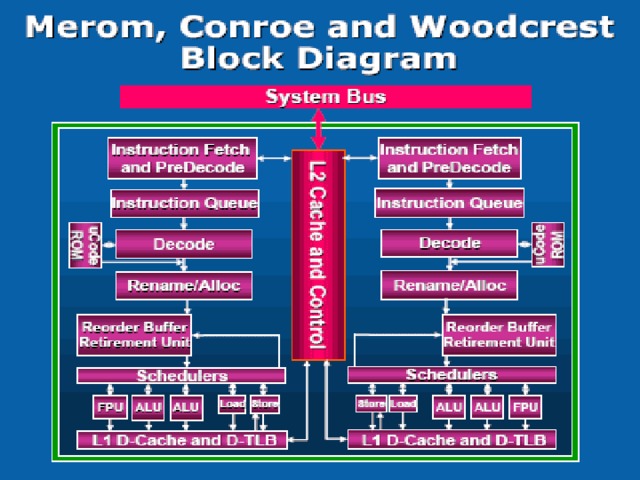

Особенности Core 2 Duo

Особенности Core 2 Duo

объём кэш-памяти при динамическом отключении другого ядра.

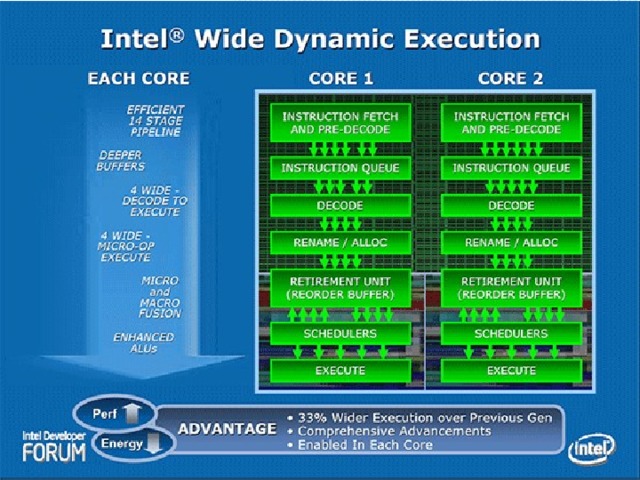

Intel Wide Dynamic Execution

Intel Advanced Smart Cache

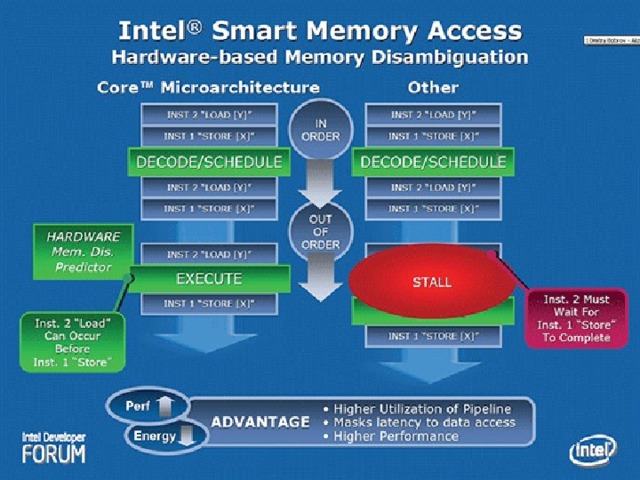

Intel Smart Memory Access

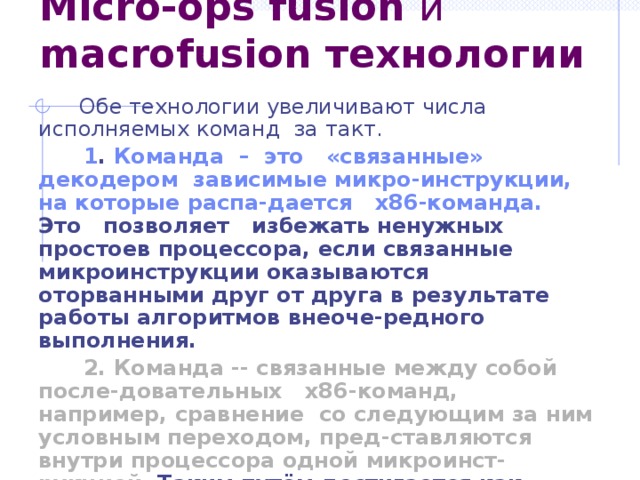

Micro-ops fusion и macrofusion технологии

Обе технологии увеличивают числа исполняемых команд за такт.

1 . Команда – это «связанные» декодером зависимые микро-инструкции, на которые распа-дается x86-команда. Это позволяет избежать ненужных простоев процессора, если связанные микроинструкции оказываются оторванными друг от друга в результате работы алгоритмов внеоче-редного выполнения.

2. Команда -- связанные между собой после-довательных x86-команд, например, сравнение со следующим за ним условным переходом, пред-ставляются внутри процессора одной микроинст-рукцией. Таким путём достигается как увеличение темпа исполнения кода, так и некоторая экономия энергии.

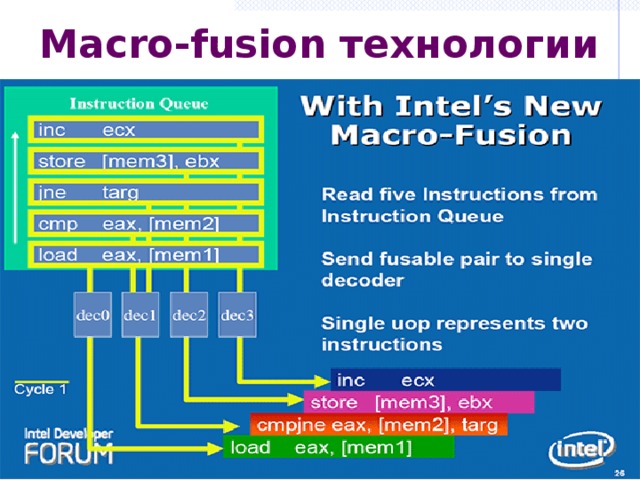

Macro-fusion технологии

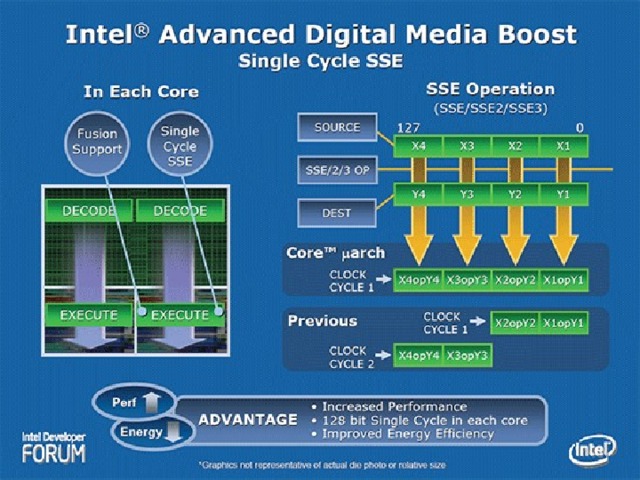

Intel Advanced Digital Media Boost

Современное ПО позволяет работать со 128-битовыми операндами различного характера (векто-рами и целочисленными либо вещественными данными повышенной точности).

Этот факт заставил инженеров Intel задуматься об ускорении работы SSE блоков процессора, тем более что до настоящего времени процессоры Intel испол-няли одну SSE-инструкцию , работающую с 128-битными операндами, лишь за два такта .

Один такт тратился на обработку старших 64 бит .

Второй такт – на обработку младших 64 бит .

Микроархитектура Core позволяет ускорить работу с SSE инструкциями в два раза .

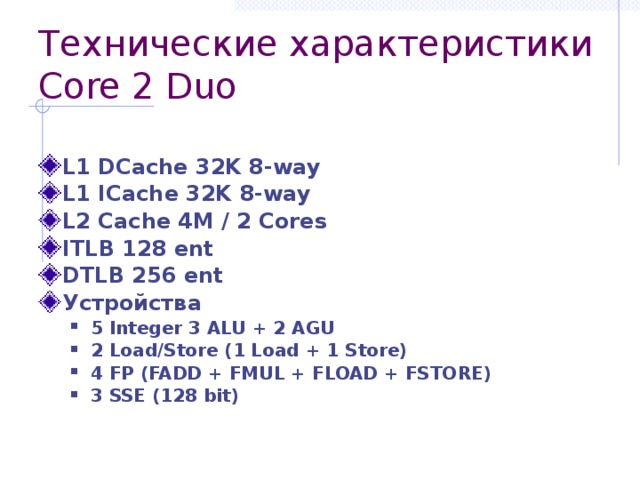

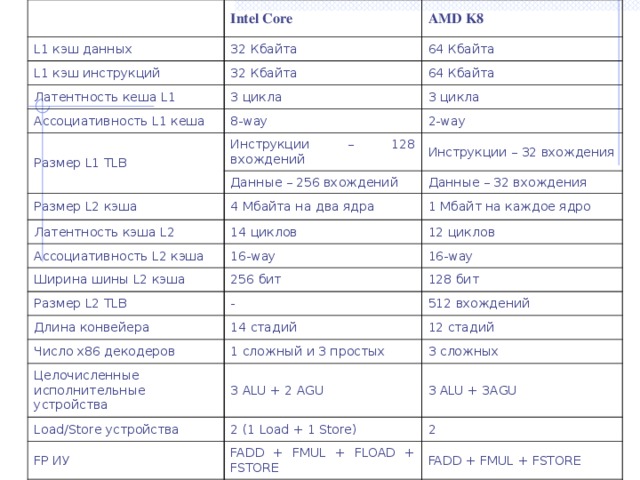

Технические характеристики Core 2 Duo

Intel Core

L1 кэш данных

32 Кбайта

AMD K8

L1 кэш инструкций

64 Кбайта

32 Кбайта

Латентность кеша L1

64 Кбайта

3 цикла

Ассоциативность L1 кеша

Размер L1 TLB

3 цикла

8-way

2-way

Инструкции – 128 вхождений

Размер L2 кэша

Инструкции – 32 вхождения

Данные – 256 вхождений

Латентность кэша L2

Данные – 32 вхождения

4 Мбайта на два ядра

Ассоциативность L2 кэша

1 Мбайт на каждое ядро

14 циклов

Ширина шины L2 кэша

16-way

12 циклов

Размер L2 TLB

16-way

256 бит

Длина конвейера

128 бит

-

Число x86 декодеров

512 вхождений

14 стадий

Целочисленные исполнительные устройства

1 сложный и 3 простых

12 стадий

Load/Store устройства

3 сложных

3 ALU + 2 AGU

FP ИУ

3 ALU + 3AGU

2 (1 Load + 1 Store)

2

FADD + FMUL + FLOAD + FSTORE

SSE ИУ

FADD + FMUL + FSTORE

3 (128-битные)

3 (64-битные)

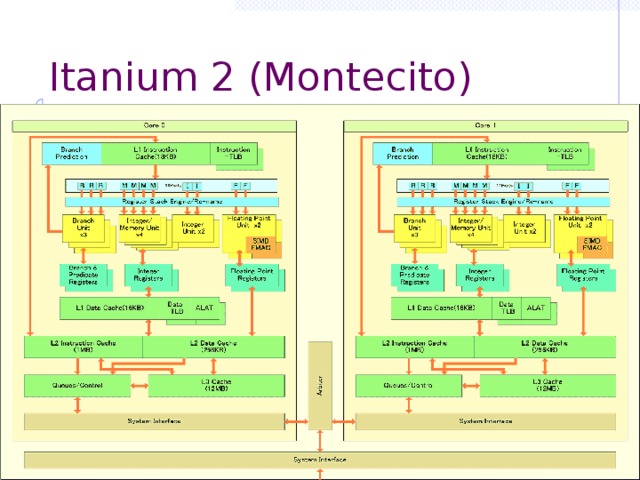

Itanium 2 (Montecito)

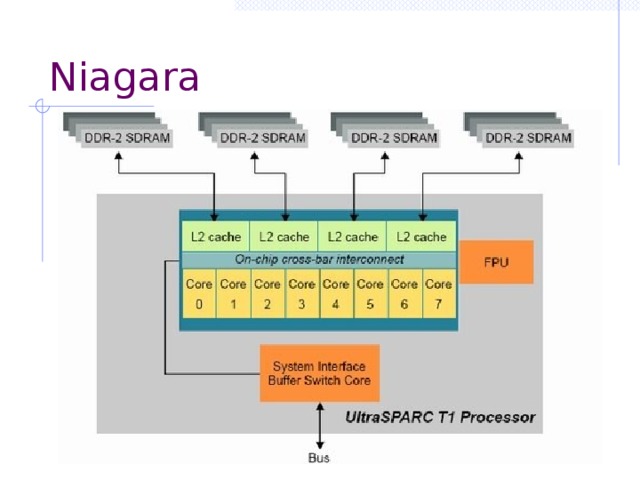

Niagara

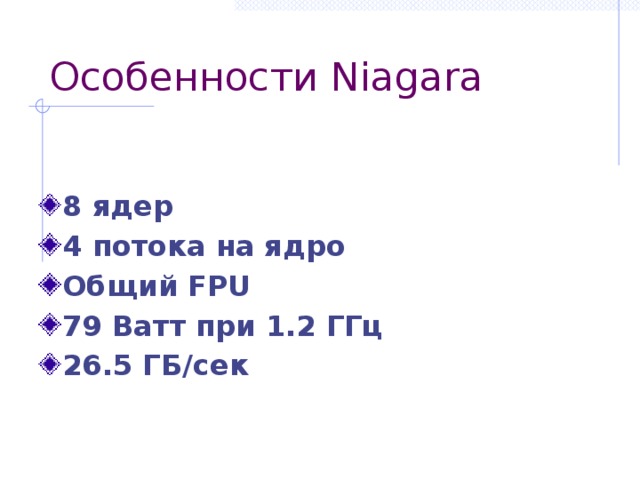

Особенности Niagara

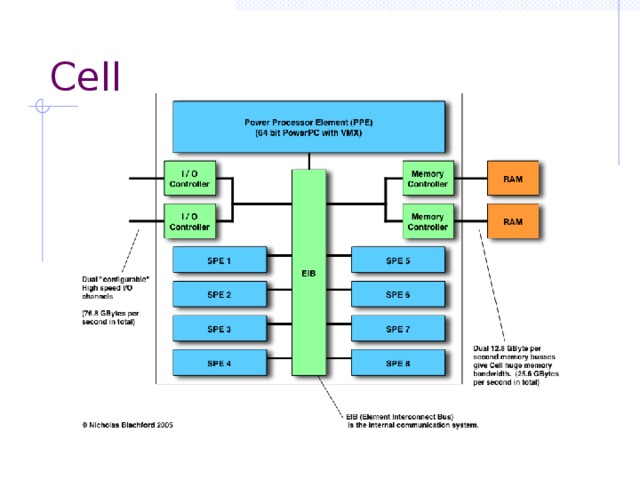

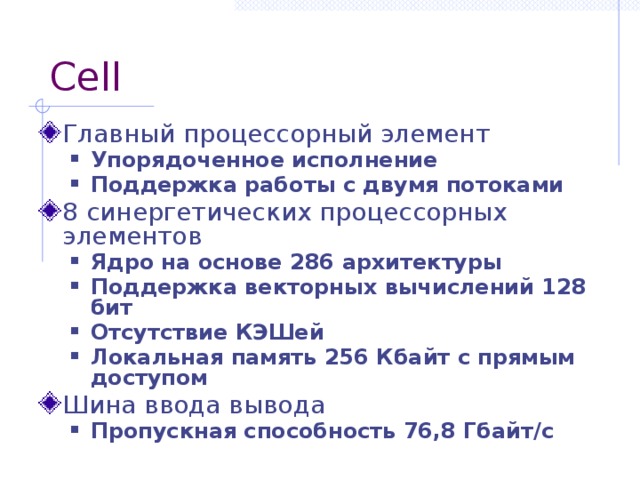

Cell

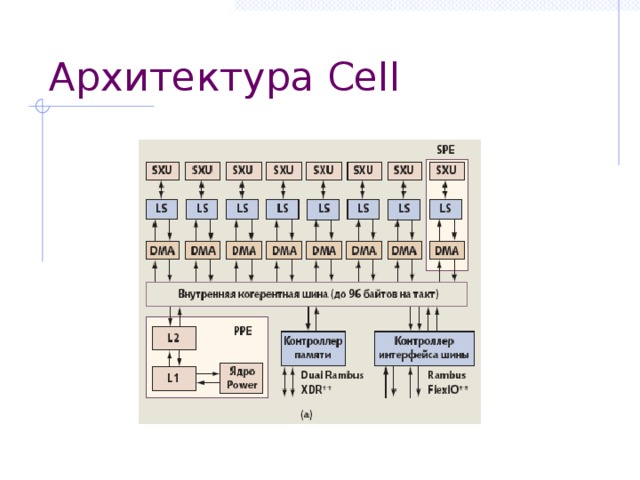

Архитектура Cell

Cell

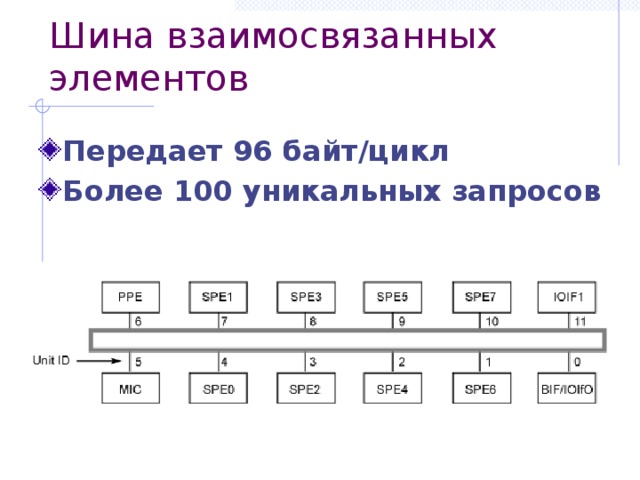

Шина взаимосвязанных элементов

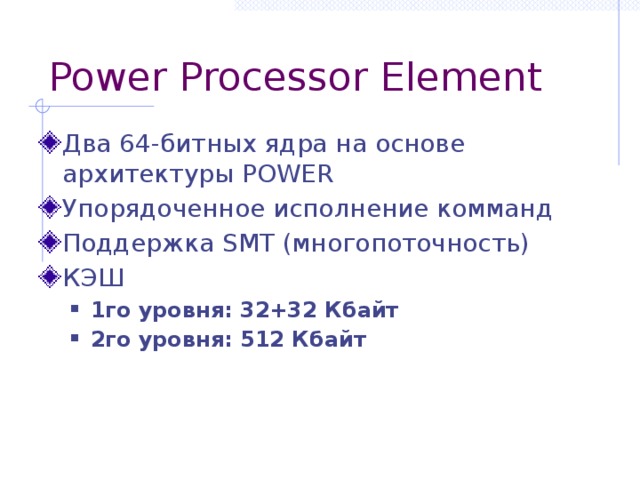

Power Processor Element

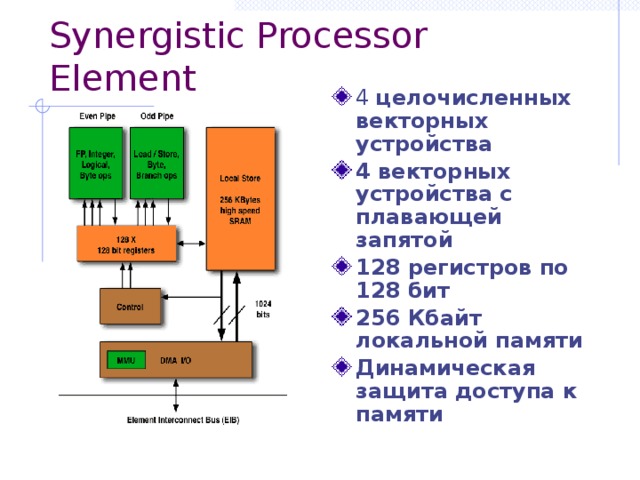

Synergistic Processor Element

Производительность Cell (для 4GHz)

THE END

-80%

-80%

0

0 596

596 38

38 Нравится

0

Нравится

0