Арифметическо – логическое устройство

Мотивация. Арифметическо - логическое устройство (АЛУ) является центральным узлом любого процессора автоматических и вычислительных средств. Оно выполняет все виды арифметических и логических операций над данными, подлежащими обработке и исполнению. Поэтому изучение принципа действия и построения АЛУ имеет для специалистов автоматических систем управ-ления крайне важное значение.

Цель занятия: изучение принципа выполнения арифметических операций сложения и вычитания, а так же логических операций над данными, представленными в виде двоичных чисел на основе использования ИМС средней степени интеграции типа К155ИП3.

Студент должен знать:

Назначение и использование АЛУ.

Принцип построения и работы много разрядных сумматоров последовательного и параллельного действия.

Принцип перевода процесса вычитания в

арифметическую операцию сложения.

Назначение знакового разряда двоичных чисел.

Принцип управления арифметическо- логическим устройством.

Перевод десятичных чисел в двоичные с присвоением знакового разряда.

Образование чисел в прямом, допол-нительном и инверсном кодах.

Выполнение арифметических операций над двоичными числами в прямом, дополнительном и инверсном кодах.

Студент должен уметь:

Осуществлять перевод десятичных чисел в двоичные в прямом коде.

Устанавливать значение знаковых разрядов двоичных чисел.

Переводить двоичные числа с прямого кода в инверсный.

Образовывать дополнительный код двоичных чисел.

Выполнять арифметические операции над двоичными числами в прямом, инверсном и дополнительном коде.

Определять назначение и функциональные возможности арифметическо-логических устройств.

Выполнять арифметические операции над

операндами с помощью АЛУ.

Производить логические операции над операндами с помощью АЛУ.

Оценивать быстродействие АЛУ при совершении арифметических операций.

Вопросы для подготовки к занятию:

а) по базисным знаниям:

Что такое арифметическо-логическое устройство?

Для каких целей служит АЛУ?

Что следует понимать под арифметической и логической операциями?

Достоинства и недостатки сумматоров последовательного и параллельного прин-ципов действия?

Как учитывается информация о знаке числа в суммирующем устройстве?

Почему операция вычитания в АЛУ заменяется операцией сложения?

Для чего используются операции сдвига в АЛУ?

Каким образом можно оценить быстро-действие АЛУ при выполнении операции суммирования?

Можно ли оценить быстродействие АЛУ в режиме выполнения операции вычитания?

Что подразумевается под логической операцией “сложение по mod2”?

Можно ли установить функциональные возможности АЛУ по его графическому обозначению?

Каким образом можно построить много разрядные АЛУ на основе ИС К155ИП3?

б) по теме занятия:

Изучить принцип действия много-разрядных сумматоров последовательного и параллельного действия.

Изучить методику выполнения ариф-метических операций над двоичными числами.

Освоить методику исследования АЛУ в режимах выполнения арифметических и логических операций.

Оценить, сколько операции вида А+В можно выполнить на таком АЛУ за 1 сек.

Научиться определять функциональные возможности АЛУ по графическому изображению.

Освоить методику проверки быстро-действия АЛУ в динамическом режиме.

Подготовить отчет по теме выполненной работы.

Краткое содержание работы

Арифметическо - логическое устройство (АЛУ) – многофункциональное устройство, в котором над двумя входными числами А и В могут быть выполнены различные логические и арифметические операции. Важнейшим узлом АЛУ является многоразрядный сумматор. В зависимости от характера ввода – вывода чисел и организации переносов, многоразрядные сумматоры бывают последовательного и параллельного принципов действия. В последовательном сумматоре сложение чисел осуществляется поразрядно, начиная с младшего разряда, с помощью сумматора на три входа. Образующийся в данном разряде перенос Рi+1 задерживается на некоторое время и поступает на вход Рi сумматора в момент прихода следующего разряда слагаемых. Т.о., производится последовательное сложение чисел - разряд за разрядом. Достоинство последовательного сумматора-простота аппара-турной реализации, недостаток- большое время суммирования.

Существенное ускорение операции сложения может быть достигнуто в сумматоре параллельного действия. Операнды поступают на входы такого сумматора одновременно по всем разрядам. Для этого в каждом разряде используется комбинационный сумматор на три входа, вырабатывающий в своих выходах сигнал суммы Si в данном разряде и переноса Рi+1 в старший разряд. В процессе распространения переноса будет устанавливаться окончательное значение суммы в каждом разделе.

Рассмотрим операцию сложения двух чисел в самом общем виде пологая, что любое из этих чисел может быть как положительным, так и отрицательным. При этом операцию вычитания можно заменить операцией сложения положительного и отрицательного числа, т.е. а - в = а + (-в). Встает вопрос о том, как передать информацию о знаке числа. Его можно решить путем использования специального разряда, называемого знаковым, которого располагают слева от основных разрядов числа. Если число положительное, знаковый разряд принимает нулевое значение, а при отрицательном числе ему присваивается единица. Для удобства анализа можно отделить знаковый разряд от основных разрядов фиксированной точкой. Знаковые разряды участвуют в арифметических операциях на равных правах с остальными, а именно, в эти разряды может производиться перенос и из этих разрядов может распространяться перенос. Перед выполнением операции сложения, устройство управления производит анализ операндов и если число положительное, оно поступает в сумматор в прямом коде, а если отрицательное - в инверсном коде. В результате сложения могут возникнуть ситуации, когда значение знакового разряда Z будет равно “0”, либо - “1”. Кроме того, возможен перенос из знакового разряда (Р=1) или отсутствия такового (Р=0). Т.о., возможны четыре следующих случая, когда:

1. Z=0; P=0; 3. Z=0; P=1;

2. Z=1. P=0; 4. Z=1; P=1;

Результат суммирования обычно записывается на хранение в регистр суммы. В первом случае (Z=0; P=0) результат операции вместе со знаковым разрядом переписывается в регистр суммы в прямом коде. Во втором случае (Z=1; P=0) результат операции вместе со знаковым разрядом переписывается в регистр суммы в инверсном коде. В третьем случае (Z=0; P=1) выполняется перенос “1” из знакового разряда в младший разряд, после чего полученный результат вместе со знаковым разрядом переписывается из сумматора в регистр суммы в прямом коде. В четвертом случае (Z=1; P=1) выполняется перенос “1” из знакового разряда в младший разряд, после чего полученный результат вместе со знаковым разрядом переписывается в регистр суммы в обратном коде. Поясним изложенное примерами.

Пусть необходимо сложить десятичные

числа Х10 = +3; У10 = +6; В оперативной памяти эти числа хранятся в прямом коде и поступают на регистры в виде: Х = 0.00011; У = 0.00110. Устройство управления после анализа знаковых разрядов передаст эти числа в сумматор в прямом коде. В результате сложения на сумматоре получается положительное число без переноса со знакового разряда Х + У = 0.01001, которые в соответствии с условием (1) поступает в регистр суммы в прямом коде, что соответствует “+9”.

Пусть требуется сложить два числа Х= +3; У= -6. В оперативной памяти эти числа хранятся в прямом коде:

Х = (+3)10 = (0.00011)2;

У = (-6)10 = (1.00110)2.

Устройство управления после анализа знаковых разрядов передаст в сумматор числа в следующем виде: Х=0.00011; У=1.11001. После выполнения сложения результат получается в отрицательном коде без переноса (Z=1;P=0): Х+У=1.11100, что соответствует ситуации (2). Следовательно, в регистр суммы запишется код 1.00011, что соответствует - 3.

Пусть складываются два числа Х = -3; У = -6; которые хранятся в оперативной памяти в прямом коде Х=1.00011; У=1.00110. После анализа эти числа поступают в сумматор в инверсном коде Х=1.11100; `У=1.11001 с сохранением значений знаковых разрядов. В результате сложения в сумматоре получается результат:

1.11100

+ 1.11001

1.10101

1

1.10110,

соответствующий ситуации (4), когда Z=1; P=1, который запишется в регистр суммы в инверсном коде с сохранением знакового разряда 1.01001, что соответствует “-9”.

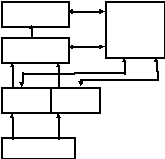

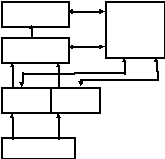

Блок - схема АЛУ представлена на рисунке 1.

| Рисунок 1. Блок-схема арифметическо- логического устройства. |

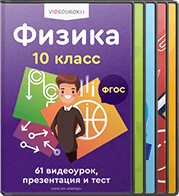

В настоящей работе будет изучено АЛУ, выполненное на основе ИМС типа К155ИП3, схема исследования которого представлена на рисунке 2. В соответствии с графическим изображением можно указать на следующие функциональные особенности АЛУ:

- А1¸А4 – информационные входы первого 4-х разрядного операнда (А);

- В1¸В4 - информационные входы второго 4-х разрядного операнда (В);

- S0¸S3 –входы, по которым осуществляется задание функции;

- Р – вход “переноса”, используемый в тех слу-

чаях, когда производятся операции над числами, с разрядностью больше четырех;

- М - вход, по которому осуществляется установка режима работы АЛУ: при М = 0

выполняется режим арифметических операций; при М=1- режим логических функций;

- F1¸F4 – информационные выходы;

- CR – выход переноса в старший разряд.

В таблицах 1 и 2 приведены все необходимые сведения для выполнения арифметических и логических операций над числами с помощью данного АЛУ. С помощью этой ИМС можно построить АЛУ с разрядностью, кратной четырем.

![]()

Примечание: 1) Символ “х” означает любое значение “0” или “1”; 2) знак Å обозначает суммирование по mod2 (0+0=0; 0+1=1; 1+1=0).

Порядок выполнения работы

Задание 1

Монтаж и исследование АЛУ на основе ИМС типа К155ИПЗ

Изучить принцип действия много разрядного сумматора последовательного и параллельного действия.

Изучить методику выполнения арифметических операций над двоичными числами в сумматоре.

Смонтировать схему исследования АЛУ на ИМС типа К155ИП3 по рисунку 2.

Приклеить к органам управления бумажный шаблон с указанием задаваемых функций.

После проверки правильности монтажа, включить блок питания стенда.

Задавая различные значения операндов, исследовать работу АЛУ в режиме выполнения арифметических операций по таблице 1. Задание функции по входам S0 ¸S3 производить путем подключения их через расширители ХР1¸ХР4 к блокам “лог.1” и “лог.0”.

Перевести АЛУ в режим выполнения логи-

ческих операций.

Таблица 1 истинности АЛУ в режиме арифметических операций

| п.п. | Арифметические операции |

| М | Р | S3 | S2 | S1 | S0 | Опе-рации |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | А+1 |

| 2 | 0 | 1 | 0 | 0 | 0 | 0 | А |

| 3 | 0 | 0 | 0 | 0 | 1 | 1 | 0000 |

| 4 | 0 | 1 | 0 | 0 | 1 | 1 | 1111 |

| 5 | 0 | 0 | 0 | 1 | 1 | 0 | А-В |

| 6 | 0 | 1 | 0 | 1 | 1 | 0 | А-В-1 |

| 7 | 0 | 0 | 1 | 0 | 0 | 1 | А+В+1 |

| 8 | 0 | 1 | 1 | 0 | 0 | 1 | А+В |

| 9 | 0 | 0 | 1 | 1 | 0 | 0 | А+А+1 |

| 10 | 0 | 1 | 1 | 1 | 0 | 0 | А+А |

| 11 | 0 | 0 | 1 | 1 | 1 | 1 | А |

| 12 | 0 | 1 | 1 | 1 | 1 | 1 | А-1 |

В соответствии с таблицей 2 исследовать работу АЛУ в режиме выполнения логических операций при различных значениях Аi и Вi. Во всех случаях значения слагаемых А и В задавать самостоятельно.

Выключить блок питания стенда, но схему не демонтировать.

Таблица 2 истинности АЛУ в режиме логических операций

| п.п. | Логические функции |

| М | Р | S3 | S2 | S1 | S0 | Опе- рации |

| 1 | 1 | х | 0 | 0 | 0 | 0 | ![]()

|

| 2 | 1 | х | 0 | 0 | 0 | 1 | ![]()

|

| 3 | 1 | х | 0 | 0 | 1 | 0 | ![]()

|

| 4 | 1 | х | 0 | 0 | 1 | 1 | 0 |

| 5 | 1 | х | 0 | 1 | 0 | 0 | ![]()

|

| 6 | 1 | х | 0 | 1 | 0 | 1 | ![]()

|

| 7 | 1 | х | 0 | 1 | 1 | 0 | ![]()

|

| 8 | 1 | х | 0 | 1 | 1 | 1 | ![]()

|

| 9 | 1 | х | 1 | 0 | 0 | 0 | ![]()

|

| 10 | 1 | х | 1 | 0 | 0 | 1 | ![]()

|

| 11 | 1 | х | 1 | 0 | 1 | 0 | В |

| 12 | 1 | х | 1 | 0 | 1 | 1 | АВ |

| 13 | 1 | х | 1 | 1 | 0 | 0 | 1 |

| 14 | 1 | х | 1 | 1 | 0 | 1 | ![]()

|

| 15 | 1 | х | 1 | 1 | 1 | 0 | ![]()

|

| 16 | 1 | х | 1 | 1 | 1 | 1 | А |

Задание 2

Оценка быстродействия АЛУ.

Оценку быстродействия АЛУ на ИМС необходимо проводить при выполнении операции А+В в наиболее “неблагоприятном” случае, когда имеется максимальное число переносов. Такая ситуация возникает при А+В16, в частности, например, при А=1011 и В=0101. Для определения быстродействия ИМС на данной операции следует измерить время от момента поступления на входы последнего операнда и до момента появления сигнала переноса. Для организации этого процесса нужно обеспечить периодическое выполнение операции суммирования А+В. При этом положим постоянство операнда А=1011, т.е. А4=1, А3=0, А2=1, А1=1 и постоянство трех старших разрядов операнда В=0101, т.е. В4=0, В3=1, В2=0, а информация в первом разряде В1 периодически меняется в виде прямоугольного импульсного сигнала. В том случае, когда В1=1, при выполнении операции А+В возникает перенос:

А = 1011

+ В = 0101

![]() 10000

10000

При В = 0 перенос не возникает:

А = 1011

+ В = 0100

![]() 1111

1111

Переменную, т.е. импульсную информацию в разряде В1 можно получить с помощью генератора импульсных сигналов. Измерив интервал времени от момента появления положительного перепада на входе ИМС до момента возникновения сигнала на выходе переноса CR, можно оценить быстродействие ИМС К155ИП3 в режиме выполнения операции А+В. Для этой цели необходимо выполнить следующее.

Вход “Зап.1” генератора соединить перемычкой с любым свободным контактом группы “лог.1”.

Вход “Свн” генератора соединить с конденсатором С5 блока дискретных элементов.

Выход “Вых.1” генератора соединить с любым свободным расширителем, например ХР5.

К этому расширителю подключить “Вход УІ” осциллографа.

Поднять конец проводника со штыря тумблера SA6 и подключить его к расширителю ХР5.

“Вход У2” осциллографа подключить к выходу “CR” (перенос) микросхемы DD37 (вывод 16 ИМС К155ИП3).

Включить питание осциллографа и получить на экране две линии развертки.

Включить блок питания стенда.

Получить на экране осциллографа устойчивые изображения сигналов по двум каналам.

С максимальной точностью измерить

интервал времени от момента возник-новения сигнала на входе до момента появления сигнала на выходе “CR” микросхемы.

Выключить приборы, демонтировать схему и привести рабочее место в порядок.

Закончить работу.

Совместная работа студента с преподавателем

Преподаватель проводит проверку самостоятельной работы студентов с опросом каждого студента, выполняет обсуждение результатов СРС, дает анализ темы занятия, подробно излагает вопросы применения темы в различных устройствах автоматических средствах управления.

Контроль исходного и заключительного уровня знаний

При закреплении пройденной темы преподаватель может задать студентам контрольные вопросы такого характера, которые непосредственно или косвенно относятся к изучаемой теме, стимулируют поиску оригинальных ответов, способствуют мысленно заново проигрывать тот или иной пункт эксперимента, чтобы оживить его перед своим взором и осознанно ответить на заданный вопрос. Например:

Доказать численно результаты выполнения арифметических операций по таблице 1.

Проверить численно результаты выполнения логических операций по таблице 2.

Литература

Калабеков Б.А. Цифровые устройства и микропроцессорные системы. -М.: Телеком. 2000.

Алексеенко А.Г., Шатурин И.Н. Микросхемотехника. - М.: Мир.1982.

Преснухин Л.Н. Расчет элементов цифровых устройств. - М.: Мир. 1982.

Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов. -М.: Радио и связь. 1988.

Компьютеры (Справочное руководство). - М.: Мир.1986.

Партала О.Н. Цифровая электроника. - С.- Пб.: Наука и техника. 2000.

Мукашев К.М., Шадинова К.С., Андаспаева А.А. Основы автоматики и микроэлектроники. Лабораторный практи-кум. Алматы, 2003 г. 162-184 стр.

Получите свидетельство

Получите свидетельство Вход

Вход

Материал по информатике на тему "Арифметическо-логическое устройство" (40.35 КB)

Материал по информатике на тему "Арифметическо-логическое устройство" (40.35 КB)

0

0 755

755 11

11 Нравится

0

Нравится

0